4. Structure of an application programming model

Application programming model

Set of logical resources presented by the computer to HLL compiler or a programmer writing the application program in assembly language

Also called 'user programming model'

Components of APM

Processor

- register set - number of registers and their functionality

- addressing modes - methods of specification of instruction arguments

- conditional operation model - implementation of conditional operation (if-then-else etc.)

- instruction set - set of operations performed by the processor

Virtual memory - The 'memory' visible in an application programming model is a virtual memory layer of memory hierarchy

- Set of virtual addresses ranges available to applications

Composition of a programming model

All components are closely connected

it is not possible to design one component independently from the others

Programming model is usually associated with underlying hardware implementation

Registers

Register functions

Accumulator - may server as both source and destination

Address register - holds address component. Specialized:

stack pointer, frame pointer, static base pointer, return address/link register

Loop iteration counter

General-purpose register - may be used as accumulator and address register

Register set architectures

Architectures without registers

Must contain 1...3 registers, including PC

Data operations 'memory to memory

Move architecture - some locations of address space implemented as registers

registers hidden behind memory locations

special register write starts arithmetic or logical operation

one location mapped to PC

Minimal register set

PC, SP, Accumulator, Address register necessary for data structure accesses

Small set of specialized registers

6...8 registers with various fixed functions

Cannot be efficiently used by compilers

example - Intel 8080/8085

Small set of general purpose registers

6...8 general purpose registers

Example - x86 in 32-bit mode

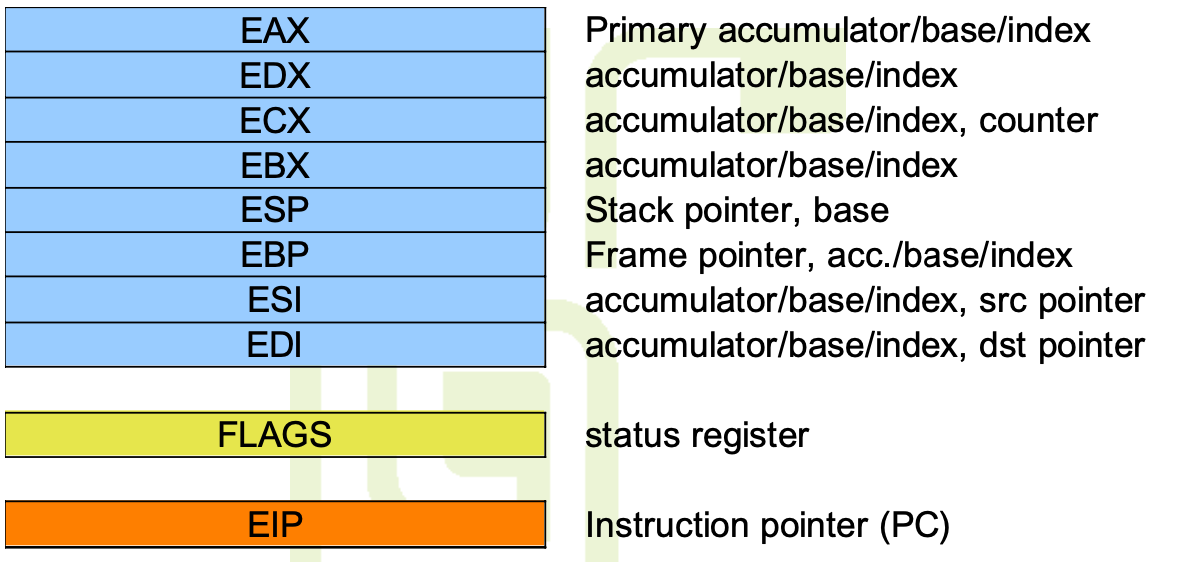

8 registers - EAX, EDX, ECX, EBX, ESP, EBP, ESI, EDI

All registers can be used as accumulators and address registers, all except ESP as index registers

3...4 registers may be used for storing local variables of arguments

Big set of general purpose registers

16 or 32 general purpose registers

Registers are used for argument passing and local variable storage

Top-of-stack buffer

Big set of g.p. registers (32...128) designed to store major part of a stack frame (excluding structures)

Subroutine's body may be executed practically without memory references

Stack-based register set

Stack of 3...8 registers

Registers may have no names

All operations performed on top of stack

no explicit arguments or single argument

arguments popped from stack, result pushed onto

Addressing modes

Method of computing the address of a memory argument

Addressing modes not referencing memory

Register direct - argument contained in a register

mov eax, ecx

Immediate - data value (constant) contained in the instruction

mov eax, 123

Register indirect modes

Argument in memory, address of argument or its component placed in register

The register containing address - base register

Variants:

- Simple r.i. - address in a register

mov eax, [ebx] - r.i. with displacement - sum of register content and a constant

mov eax, [ebx + 4] - double-register indirect - sum of two register

mov eax, [ebx + ecx]

Minimal set of addressing modes

Only three addressing modes are necessary for efficient implementation of HLLs:

- Register direct

- Immediate

- One of r.i. modes (usually r.i. with displacement)

Absolute (direct) mode

Data in memory, address contained in the instruction

mov eax, [x]

x is a name of variable, converted by assembler into a constant address value

the easiest method of static data addressing

unnecessary - may be replaced by r.i. with displacement

PC-based modes

r.i. using PC as base register

Indexed modes

Address obtained by adding the address generated using some of the previously presented memory addressing modes and value of index register, optionally multiplied by a constant scale factor (power of 2)

mov eax, [ebx + ecx * 4]

register is called index register

scale - 1, 2, 4, 8, or 16

Multiplication implemented as left-shifting

Scale == 1 - double register indirect mode

Scale != 1 - scaled index mode

Examples

[table + ecx * 4] - absolute indexed

[ebx + edx * 2] - register indirect indexed

Register indirect with base automodification

Modifies the content of a base register by adding or subtracting the size of memory data being accessed

preincrementation ++i

postincrementation i++

predecrementation --i

postdecrementation i--

Stack operations make an implicit use of these modes, for full descending stack:

PUSH - predecrementation

POP - postincrementation

Memory indirect modes

Data in memory at the address, which component is also placed in memory (pointer variable). Two references:

- To access address component (ptr var)

- To access the target data

Useful with table-of-pointers type structures

Conditional operations model

Implementation of conditional operations

Variants:

- Model with flags

- Model without flags ('compare and...')

- Predicates

Conditional operations

Describes the implementation of conditional operations

Variants:

- With flags

- Without flags

- Predicates

Conditional operations using flags

Flag - single bit register storing the attributes of the recent operation result

Available flags:

- Z - Zero

- N/M/S (Negative/Minus/Sign) - sign

- C/CY - Carry

- O/V/OV - Overflow

- AC/HC (auxiliary/half carry) - BCD carry

- P - Parity

AC/HC and Parity is not used anymore (still found in x86)

Flag setting rules

All rules are described in the processor documentation

All flags are set by basic two-argument arithmetic and logical instructions

Other instructions (like single-argument) may set only some of the flags

I

n some architectures (M68k, HC08), Zero and Sign flags are set by data transfer instructions

Intel decided not to set those flags

Special instructions may only set the flags not affecting any other registers (in x86)

- Arithmetic compare - CMP (subtraction without storing the result)

- Logical compare - TEST (logical and without result store)

Conditional instructions

Specifies the condition for its execution

Conditional jump/branches - available in almost all archs.

Conditional skip - skip the next instruction (usually in very simple archs.)

Conditional data moves - available in newer archs

Conditional set instruction

Conditional execution of all or most instructions (ex. ARM)

Conditional operations without flags

Single instruction evaluates the bool value of a relation between data and executes some operation is true

ex. "jump if two registers are equal"

Typically found in simple RISC architectures like MIPS and RISC-V

Predicates

Generalized flags, storing logical values of several previously evaluated relations or expressions

- Evaluate results of conditions in predicates:

- save a < b in pred1

- save c >= d in pred2

- save e == f in pred

- Execute based on predicates

- jump if pred2 is true

Conditional operations in vector unit

if - then - else implemented as selection between two possible results (a, b) for each vector element

x = <cond> ? a : b;

a and b vectors are computed first